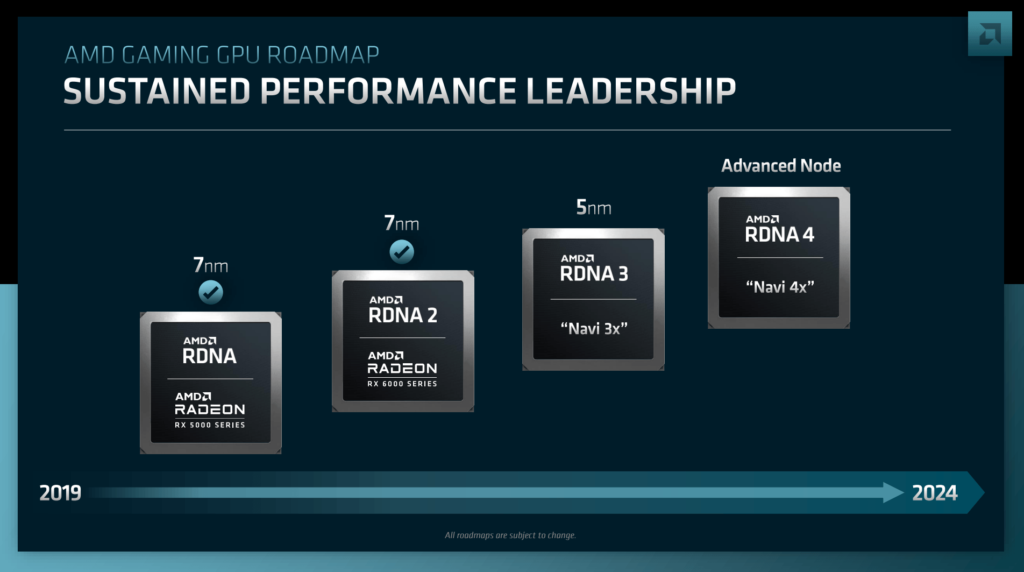

Come già sappiamo sono recentemente trapelate delle voci secondo le quali AMD starebbe pensando di non portare sul mercato architetture MCM per la prossima generazione di GPU, concentrandosi su Navi 43, che dovrebbe avere 64 CU e performance superiori a Navi 32 in un setting monolitico e Navi 44 con 32 CU per il mercato FHD/2K, sempre monolitico e con processo produttivo a 3/4nm, il 70% più denso di quello che è possibile oggi con i 5/6nm.

Questa scelta sarebbe stata forzata da diversi fattori: il mercato GPU che chiede a gran voce prodotti più “snelli”, la possibilità di essere integrati nel mercato mobile e APU con più facilità (essendo, oltretutto, più redditizio) oltre ai costi di sviluppo inferiori e tempistiche più veloci per la presentazione.

Ovviamente oggi non conosciamo che cosa AMD intenda per performance da fascia media, presumiamo che viste le migliorie tecniche, potrebbero pareggiare in raster una RX 6900, con benefici molto importanti su Ray Tracing e geometria, sempre ricordando che parliamo di prodotti di fine 2024.

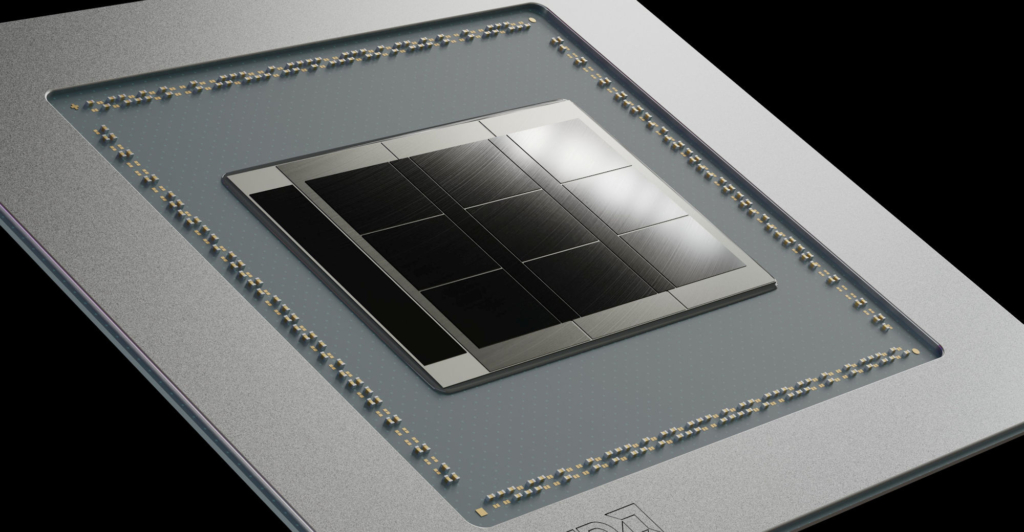

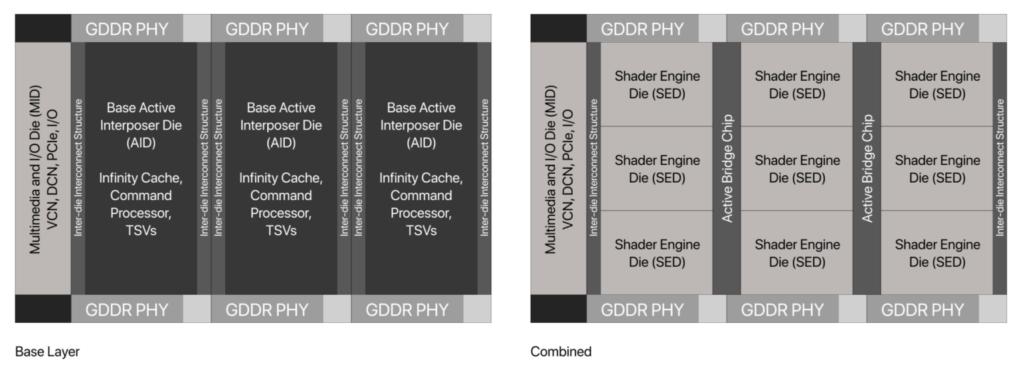

Sarebbero questi, quindi, i motivi della rinuncia, almeno per ora, allo sviluppo di Navi 41, o 4c come viene indicato in diversi leak: lo stesso si tratterebbe di un approccio realmente complicato e rivoluzionario al concetto MCM: il chip sarebbe diviso in una parte I/O e in 3 gruppi di unità di calcolo detti AID con alla base, per ognuno di essi, un quantitativo di Infinity Cache, un interposer e le logiche di controllo GDDR7 con inseriti 3 unità di calcolo shaders dette SED per ogni gruppo.

I calcoli sono presto fatti, un massimo di 9 unità SED per la versione full del Chip, probabilmente con 16 o 32 (improbabile quest’ultime) CU, il che porterebbe a una Navi 41 con un massimo di 144 CU che sarebbe poi un plausibile update dagli attuali 96 di RX 7900 XTX, mentre un eventuale Navi 42 perdendo un AID per semplificare il chip vanterebbe, comunque, 96 CU come l’ex top di gamma ma con una efficienza superiore, visto il processo produttivo, che potrebbe essere del 50-60%.

Il problema resta la complessità, in questo caso si integrerebbero dai 13 ai 20 chip sullo stesso die, considerando la parte dedicata alla memoria, utilizzando, inoltre, tecniche di Die Stacking il che si capisce rende i tempi di sviluppo, ottimizzazione, ma anche affinamento driver tediosi, senza contare i costi, che in questo caso potrebbero essere ben più sfidanti di Navi 31.

Ricordiamo, comunque, che queste restano voci di corridoio sebbene confermate da più parti, e anche la rinuncia allo sviluppo di una scheda top di gamma non è detto che poi non avverrà, è anche possibile che si concentrino primariamente sulla fascia media, per poi uscire successivamente con soluzioni più performanti.